KotiblogiSR Flip-Flop -tietoopas-työhön liittyvä periaate, edut, haitat, totuustaulukko ja erot RS-flip-flopista

SR Flip-Flop -tietoopas-työhön liittyvä periaate, edut, haitat, totuustaulukko ja erot RS-flip-flopista

Flip-flop on yksinkertaisesti termi, joka viittaa digitaaliseen elektroniseen laitteeseen, joka on elektroninen komponentti, jota käytetään yhden bitin tietojen tallentamiseen.

SR-flip-flop (set-reset-flip-flop) on digitaalisten elektronisten piirien peruskomponentti, jota käytetään tietojen tallentamiseen ja manipulointiin.Se toimii peräkkäin.SR-flip-flops voidaan rakentaa SR-salpoilla.Latch on digitaalinen elektroninen piiri, joka on tallennuselementin yksinkertainen muoto, joka pystyy tallentamaan yhden bitin binaarista tietoa (0 tai 1).Tässä artikkelissa keskustellaan SR-flip-flopista, mukaan lukien sen toimintaperiaatteet, totuustaulukko, edut, haitat ja erot RS-flip-flopista.

Luettelo

1. SR Flip-Flop -työperiaate

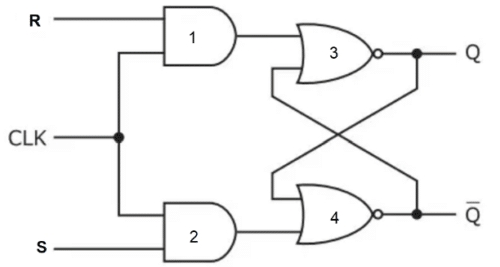

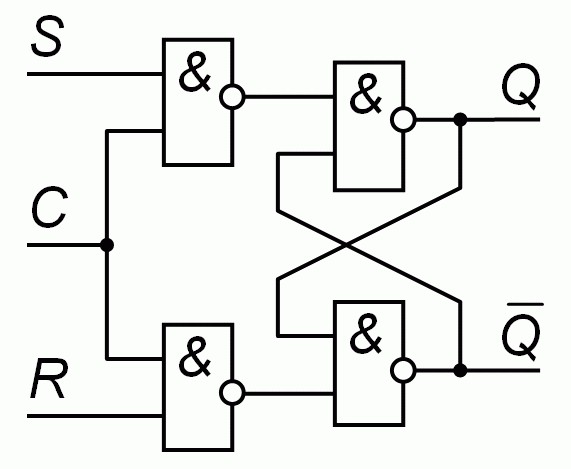

Yksinkertaisin RS-flip-flop voidaan rakentaa käyttämällä kahta 2-sisääntuloa eikä porttia, kuten kaaviossa on esitetty:

Huomaa, että elementtien kytketty tapa varmistaa, että ne ovat aina vastakkaisissa tiloissa.Jos ensimmäisen elementin lähtö on 1, toisen elementin lähtö on 0 ja päinvastoin.

Ymmärtämisen helpottamiseksi tässä on neljä skenaariota, joita voi esiintyä SR-flip-flopilla:

Skenaario 1: S = 0, r = 0

Portin lähtö: Sekä Gate1 että GATE2 -lähtö 0. Tilan ylläpito: Koska portit 3 ja 4 ovat Nortes, yhdellä tulolla 0, niiden lähtö riippuvat toisesta tulosta.Siten Gate3/Q (n+1) säilyttää edellisen tilan Q ja Gate4/Q (n+1) 'säilyttää komplementaarisen tilan q'.

Skenaario 2: S = 0, r = 1

GATE -lähtö: Gate1 -lähtö 1 (koska R on korkea), Gate2 -lähtö 0. Palautustoiminta: Gate3: lle yksi tulo on korkea (Gate1: stä), mikä johtaa 0: n lähtöön NOR -operaation kautta, siten palauttaen tila.Yksi syöttö GATE4: lle pysyy kuitenkin alhaisena, lähtö 1, mikä osoittaa täydentävän tilan.

Skenaario 3: S = 1, r = 0

Portin lähtö: Gate1 -lähtö 0, Gate2 -lähtö 1 (koska S on korkea).Aseta toiminta: Tällä hetkellä Gate3-lähtö 1 (toinen Gate1: n tulo on alhainen), asettamalla flip-flop.Sitä vastoin Gate2: n, Gate4 -lähtö 0: n korkean tuloksen vuoksi, vahvistaen täydentävän tilan.

Skenaario 4: S = 1, r = 1

Portin lähtö: Kun molemmat tulot ovat korkeat, molemmat portit lähtö 1. Virheellinen tila: Kun molemmat tulot ovat korkeat, portit 3 ja 4 molemmat lähtö 0, mikä johtaa konfliktiin, koska Q (n+1) ja Q (n+1) pitäisiolla täydentäviä lähtöjä, mutta näin ei ole, mikä johtaa siihen, että tämä tila on virheellinen.

2. SR Flip-Flop-totuustaulukko

|

S |

R - |

Q (n+1) |

Osavaltio |

|

0 - |

0 - |

Qn |

Ei muutosta |

|

0 - |

1 |

0 - |

Nollata |

|

1 |

0 - |

1 |

SARJA |

|

1 |

1 |

X |

Virheellinen |

Käytämme tätä totuustaulukkoa kirjoittaaksesi ominaispöydän SR-flip-flopille.Totuustaulukossa voit nähdä kaksi tuloa, S ja R ja yhden lähdön, Q (n+1).Ominaisuustaulukossa näet kuitenkin kolme tuloa, s, r ja qn ja yhden lähtö, Q (n+1).

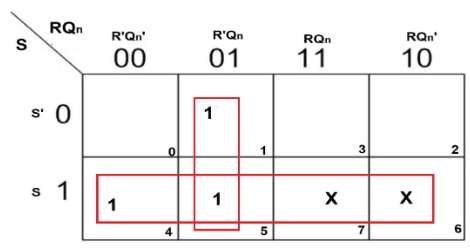

Logic-kaaviosta on selvää, että QN ja QN 'ovat kaksi komplementaarista lähtöä, jotka toimivat myös panoksina 3 ja 4: lle, joten tarkastellaan Flip-Flopin nykyistä QN: tä tuloksena ja Q (n (N+1), seuraava tila, lähtö.

Ominaisuustaulukon kirjoittamisen jälkeen piirrämme 3-muuttujan K-kartta ominaisyhtälön saamiseksi.

3. Ominaisuustaulukko

|

S |

R - |

Qn |

Q (n+1) |

|

0 - |

0 - |

0 - |

0 - |

|

0 - |

0 - |

1 |

1 |

|

0 - |

1 |

0 - |

0 - |

|

0 - |

1 |

1 |

0 - |

|

1 |

0 - |

0 - |

1 |

|

1 |

0 - |

1 |

1 |

|

1 |

1 |

0 - |

X |

|

1 |

1 |

1 |

X |

K-mapista saat kaksi paria.Ratkaistuaan molemmat saadaan seuraavan ominaisyhtälön:

Q (n + 1) = s + r'qn

4. SR-flip-flopin edut

SR-flip-flops -sovelluksella on useita etuja.Alla on joitain niistä:

- Yksinkertaisuus: SR-flip-flopsin suunnittelu on suhteellisen yksinkertainen, koostuu vain muutamasta portista.Ne voidaan helposti integroida suurempiin piireihin vaikeuttamatta yleistä suunnittelua.

- Nopeus: SR-flip-flops toimii suurella nopeudella.Ne voivat vaihtaa nopeasti asetettujen ja nollaustilojen välillä ilman viivettä, varmistaen, että digitaaliset järjestelmät voivat suorittaa tehtäviä tehokkaammin parantaen siten nopeaan tietojenkäsittelyyn perustuvien tekniikoiden suorituskykyä.

- Pieni virrankulutus: SR-flip-flops kuluttaa hyvin vähän virtaa, mikä tekee niistä ihanteellisia käytettäväksi akkukäyttöisissä laitteissa, kuten matkapuhelimissa ja kannettavissa laskentalaitteissa, samalla kun se tarkoittaa myös alhaisempia toimintakustannuksia energiankäytön suhteen.

- Bistable-toimenpide: SR-flip-flops voi ylläpitää tilaa määräämättömäksi ajaksi (asetettu tai nollata), kunnes tulosignaali kehottaa muutoksen ja kyky ylläpitää vakaa tila ilman vakiotuloa tekee SR-flip-flopsista hyödyllisen eri sovelluksissa.

5. SR-flip-flops-rajoitukset

Useista eduista huolimatta SR-flip-flopsissa on myös joitain rajoituksia.Alla on joitain niistä:

- Kilpailuolosuhteet: SR-flip-flops ovat alttiita rotuolosuhteille, joissa lähtötila voi muuttua arvaamattomasti syöttösignaalien ajoituksen muutoksista, mikä mahdollisesti johtaa virheisiin tai odottamattomiin tuloksiin.

- Virheellinen tila: SR-flip-flopsin luontainen rajoitus on niiden käyttäytyminen, kun sekä asetukset (S) että nollaus (R) -tulot ovat aktiivisia samanaikaisesti.Tässä tapauksessa flip-flop tulee virheelliseen tilaan, mikä johtaa usein siihen, että molemmat tuotokset ovat korkeat tai matalat, mikä rikkoo bistable-laitteen perusperiaatetta.Tämä virheellinen tila voi häiritä digitaalisten piirien normaalia toimintaa, mikä johtaa arvaamattomaan järjestelmän käyttäytymiseen ja mahdollisiin tietojen menetyksiin.

- Rajoitettu skaalautuvuus: SR-flip-flops voi olla vaikea skaalata monimutkaisempiin digitaalisiin järjestelmiin, kun järjestelmän monimutkaisuus kasvaa, myös SR-flippien perusluonteen aiheuttamien virheiden aiheuttamisen todennäköisyys kasvaa.

6. Sovellusalueet

- Ohjausjärjestelmät: Ohjausjärjestelmissä SR-flip-flops voi saavuttaa signaalien välillä sujuvat siirtymät, minimoimalla onnettomuuksien riskit ja parantaa liikennevirtaa.Yleinen sovellus on liikenteen valonhallintajärjestelmissä, joissa SR-flip-flops auttaa hallitsemaan liikennevalojen sekvenssiä, varmistaen, että signaalit muuttuvat tarkasti ja järjestetyllä tavalla, siten turvallisesti ja tehokkaasti hallitsemalla liikennevirtaa.

- Muistin tallennus: SR-flip-flops ovat myös muistin tallennuslaitteiden, kuten rekistereiden, peruskomponentteja.Niitä käytetään tietojen väliaikaisesti tietojen tallentamiseen laskentalaitteisiin, jotka vaihtelevat mikroprosessoreista digitaalisiin signaalin prosessoriin, mikä mahdollistaa tietojen nopean pääsyn ja manipuloinnin prosessointitehtävien aikana.

- Digitaaliset laskurit: SR-flip-flopsia käytetään digitaalisissa laskureissa laskentatoimintoihin, mikä mahdollistaa lisäämisen tai pienenemisen syöttösignaalien perusteella.

- Tietojen synkronointi: SR-flip-flopsit ovat ratkaisevan tärkeitä datasignaalien synkronoimiseksi kahden digitaalisen piirin välillä, varmistaen, että ne toimivat samanaikaisesti saman kellosyklin sisällä, mikä on erittäin hyödyllistä viestintäverkkojen luotettavuuden ylläpitämiseksi.

- Oskillaattorit: Yhdistettynä muihin komponentteihin SR-flip-flops voi muodostaa yksinkertaisia oskillaattoreita, jotka tuottavat jaksollisia signaaleja.Tämä on erityisen hyödyllistä sovelluksissa, kuten kellopiireissä ja audiosignaaligeneraattoreissa, joissa tarvitaan johdonmukaista ja vakaa signaalin luomista.

7. Erot SR: n ja RS-flip-flopsin välillä

|

Ominaisuus |

SR-Flip-Flop |

Rs-flip-flop |

|

S = 0 , r = 0 |

Q Tila (ei muutosta) ylläpidetty. |

Q Tila (ei muutosta) ylläpidetty. |

|

S = 0 , r = 1 |

Nollaa (Q = 0) |

Nollaa (Q = 0) |

|

S = 1 , r = 0 |

Asetettu (q = 1) |

Asetettu (q = 1) |

|

S = 1 , r = 1 |

Asetettu (hallitseva) (q = 1) |

Nollaa (hallitseva) (Q = 0) |

|

Edut: |

Kun S ja R ovat molemmat 1, asetettu toiminta

on etusijalla. |

Kun S ja R ovat molemmat 1, nollausoperaatio

on etusijalla. |