KotiblogiYksityiskohtainen opas täyteen lisäaineen

Yksityiskohtainen opas täyteen lisäaineen

Digitaalisen elektroniikan ja tietokonetekniikan alueella lisäosat edustavat yhtä tärkeimmistä rakennuspalikoista, jotka ovat keskeisiä monimutkaisempien aritmeettisten piirien rakentamisessa ja toiminnallisuudessa.Aritmeettisen logiikkayksikön (ALU) integraalikomponentteina Adders helpottaa lukuisia laskentatoimintoja, jotka vaihtelevat aritmeettisesta perus- ja monimutkaiseen loogiseen tehtäviin, joita tarvitaan järjestelmäoperaatioihin.Heidän suunnittelunsa, joka voi vaihdella yksinkertaisesta puolijalkaisuudesta monimutkaisempiin täyden lisäaineisiin, on tärkeä rooli digitaalisten järjestelmien prosessoinnin tehokkuuden ja nopeuden parantamisessa.Tämä artikkeli pohtii erityyppisten lisäosien yksityiskohtaista arkkitehtuuria ja funktionaalisia vivahteita, jotka kuvaavat niiden kriittistä roolia nykyaikaisessa laskentatekniikassa ja tutkimalla niiden toimintalogiikkaa, piiriä ja sovelluksia digitaalisen logiikan suunnittelun laajemmassa yhteydessä.

Luettelo

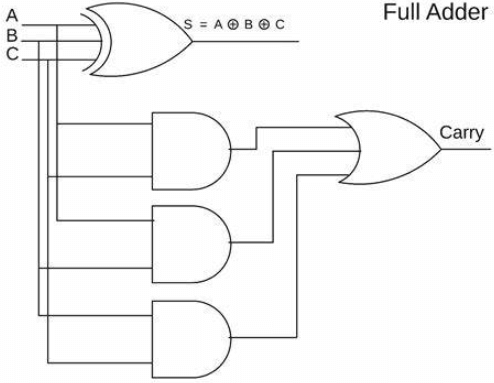

Kuva 1: Täysi lisäys

Adder on tärkeä osa elektronista tekniikkaa ja digitaalista logiikan suunnittelua, ja sillä on keskeinen rooli monimutkaisemmissa tietokonejärjestelmissä.Osana aritmeettista logiikkayksikköä (ALU) Adder hoitaa erilaisia välttämättömiä laskentatoimia.Koko prosessorin tehokkuuteen ja suorituskykyyn vaikuttavat suoraan lisäaineen suunnitteluun ja toiminnallisuuteen.

Prosessorissa lisäystä ei käytetä pelkästään aritmeettisten operaatioiden, kuten lisäyksen ja vähentämisen, vaan myös laajemman loogisten toimintojen laajempaan valikoimaan.Esimerkiksi ohjelmia suoritettaessa prosessorin on usein laskettava uudet muistiosoitteet.Tämä tehdään tyypillisesti lisäämällä tai vähentämällä nykyinen osoite - lisäysten suorittama tehtävä.Ne hallitsevat silmukka -iteraatioiden lukumäärää ja yleistä virtausta lisäämällä ja vähentämällä laskureita.Monimutkaisemmissa sovelluksissa, kuten taulukon indeksointi, Adders etsi tiedot nopeasti laskemalla siirrot.Tämä on tärkeää tietokannan hallintajärjestelmille, kääntäjän rakentamiselle ja laajamittaiselle tietojenkäsittelylle.Lisäaineet ovat avainasemassa myös tiettyjen kartoitustekniikoiden toteuttamisessa monitasoisissa välimuistijärjestelmissä, käyttämällä aritmeettisia toimintoja välimuistin datan sijainnin määrittämiseksi, mikä optimoi pääsyn tehokkuuden.

Teknologisesti lisäosat toteutetaan erilaisten piirimalleiden kautta, mukaan lukien rinnakkais-, sarja- ja putkilinjan lisäosat.Rinnakkaislisät ovat suosittuja niiden kyvystä käsitellä useita numeroita samanaikaisesti, mikä tekee niistä sopivia nopeaan laskentaan vaativiin tilanteisiin.Sarja-lisäosat toisaalta prosessoivat yksi bitti kellosykliä kohti ja ovat ihanteellisia resurssirajoitettuihin tai pienitehoisiin ympäristöihin.Putkilinjan lisääjät jakavat lisäysprosessin useisiin vaiheisiin, joista kukin käsittelee osan lisäyksen operaatiosta.Tämä malli lisää merkittävästi laskentanopeutta, etenkin korkean suorituskyvyn laskentaympäristöissä.

Puoli-syöttöpiiri on digitaalisen elektroniikan perustavanlaatuinen rakennuspalikka, joka on erityisesti suunniteltu lisäämään kaksi yksittäistä binaarinumeroa.Tämä piiri muodostaa täydellisen lisäaineen perustan ja on avain monimutkaisempien logiikkapiirimalleiden ymmärtämiseksi.Puolikerroksessa on kaksi ensisijaista tuloa, merkitty A ja B, jotka edustavat vastaavasti Augeneaa ja lisäystä.Tämän asennuksen avulla se voi laskea summan ja kuljettaa lähtöä ilman, että edellisistä laskelmista on tarvetta kuljetustuloa.

Puolisoidon ydin koostuu kahdesta logiikkaportista: XOR-portista ja an ja portista.XOR -portti vastaa summan ulostulon luomisesta.Se toimii yksinkertaisen säännön mukaisesti, jossa se tuottaa 1, jos vain yksi sen tuloista on 1;Muutoin se tuottaa 0. ja portti puolestaan käsittelee kantolähtöä.Se tuottaa yhden vain, kun molemmat sen tulot ovat 1, mikä vastaa täydellisesti binaarisen lisäyksen perusvaatimuksia.

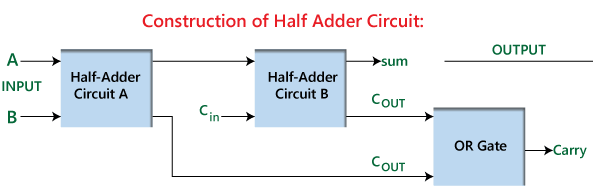

Kuva 2: Puolisoderin rakentaminen

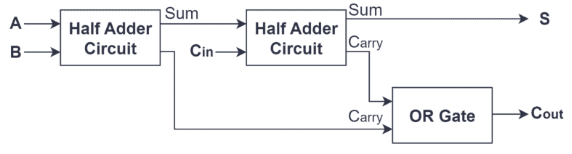

Tämä tehokas ja suoraviivainen muotoilu antaa puolikerroksen paitsi suorittaa binaarilisäyksen itsenäisesti myös rakennuspalikana täydellisen lisäaineen luomiseksi.Koko lisäys rakennetaan yhdistämällä kaksi puolikerraa lisä- tai portilla.Tässä asennuksessa ensimmäisen puoliajan lisäys ottaa alkuperäisen lisätehtävän, tuottaen alustavan summan ja kantaa.Toisen puoliajan sovitus käsittelee sitten kuljetuksen ensimmäisestä ja ylimääräisen kuljetustulon kanssa.Lopuksi OR -portti yhdistää nämä kaksi kuljetuslähtöä lopullisen kuljetuslähteen tuottamiseksi.Tämä järjestely parantaa korottajan toiminnallisuutta, mikä antaa sen käsitellä monimutkaisempia moni-bittisiä lisätehtäviä, esittäen laajalle levinneen sovelluksen ja puoleen lisäosien merkityksen digitaalisessa piirin suunnittelussa.

Täysin lisäys on digitaalisen logiikan suunnittelun edistyksellinen komponentti, joka on varustettu käsittelemään kolmen yhden bittisen binaarisyötön lisäämistä, jotka on yleisesti merkitty A-, B- ja kantolaitteiksi (CIN).Tämä malli antaa täyden lisäaineen prosessoida tehokkaasti kompleksisia binaarisia lisäyksiä sisällyttämällä kuljetus aiemmista alemman asteen laskelmista yhteen operaatioon.

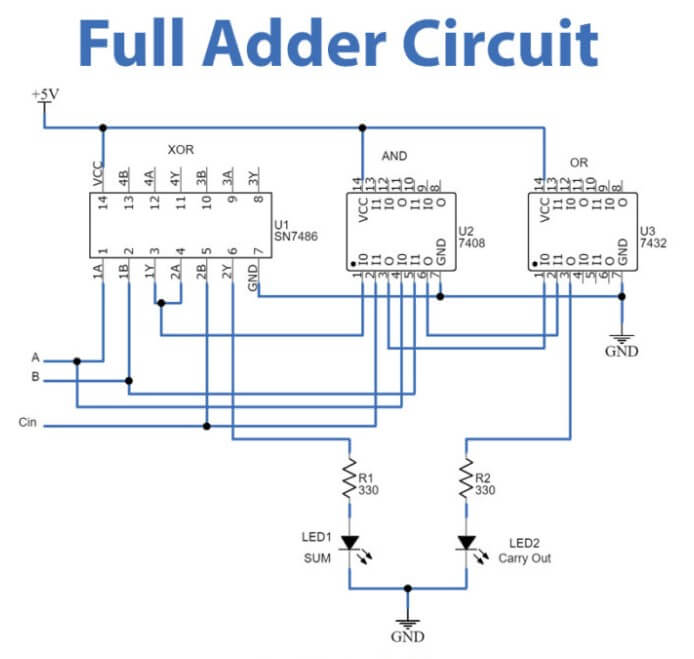

Kuva 3: Koko lisäyspiiri

Funktionaalisesti täydellinen lisäin voi tuottaa kaksinumeroisen summan, mikä tarkoittaa, että sen lähtö voi olla välillä 0-3, ja se voi myös tuottaa suorituksen (Cout).Tämä tapahtuu, koska kun kaikki syöttöbittit asetetaan arvoon 1 (a = 1, b = 1, cin = 1), summan lähtö on 1 (edustaa binaarista 01) ja luodaan 1, mikä osoittaa, että se osoittaa, että seLisäkanta on siirrettävä seuraavaan korkeampaan bittiin.

Rakenteellisesti koko lisäin koostuu yleensä kahdesta puolikerroksesta ja yhdestä tai portista.Ensimmäisen puoliajan lisäys saa tuloja A ja B, mikä tuottaa alkuperäisen summan ja kuljetussignaalin.Tätä alkuperäinen summa syötetään sitten ja kuljetus (CIN) toiseen puolisoon.Toisen puoliajan tarkkuuden tehtävänä on lisätä tämä summa ensimmäisen puoliajan lisäyksestä CIN: hen, tuottaen uuden summan ja uuden kantolähteen.Samanaikaisesti ensimmäisen puoliajan syöttötuotteen kuljetuslähtö ja toisen puoliajan lisäysten kuljetuslähtö sulautetaan tai portin läpi, huipentuen täyden lisätuimen lopulliseen suoritukseen (cout).Tämän rakenteen suunnittelu varmistaa, että täysi lisäin käsittelee tehokkaasti kuljettajien etenemistä lisäksi, mikä tekee siitä ihanteellisen monen binaaristen lisäysten suorittamiseen.Siten täyden lisäaineen suunnittelu ei vain nopeuta tietojenkäsittelyä ja parantaa tehokkuutta, vaan myös yksinkertaistaa laitteistojen toteutuksen monimutkaisuutta suoraviivaisen logiikkaporttien yhdistelmän avulla, mikä tekee siitä välttämättömän komponentin moninumeroisessa lisäyksessä ja aritmeettisessa logiikkayksikössä (ALU).

|

Parametrit

|

Puoliksi

|

Täydennys

|

|

Kuvaus

|

Puoli -adder on yhdistelmälogiikka

piiri, joka lisää kaksi 1-bittistä numeroa.Puoli-syöttö tuottaa kahdesta summan

tulot.

|

Täysin lisäys on yhdistelmälogiikka

Piiri, joka suorittaa lisäysoperaation kolmella bittisellä binaarinumerolla.

Koko lisäys tuottaa kolmen tuloksen summan ja kantoarvoa.

|

|

Edellinen kanto

|

Edellistä kantoa ei käytetä.

|

Edellistä kantoa käytetään.

|

|

Tulot

|

Puoli -lisäyksessä on kaksi syöttöbittiä (A,

B).

|

Täysin syöttöbittiä on kolme

(A, B, Csisä-).

|

|

Lähdöt

|

Luotu lähtö on kaksi bittiä

ja kantaa 2 bitin syöttöltä.

|

Luotu lähtö on kaksi bittiä

ja kantaa 3 bitin syöttöltä.

|

|

Käytettynä

|

Puoli-syöttöä ei voida käyttää

Samalla tavalla kuin täyden asteen piiri.

|

Täysia lisäyspiiri voidaan käyttää paikoillaan

puoliksi syöttöpiiristä.

|

|

Ominaisuus

|

Se on yksinkertainen ja helppo toteuttaa

|

Täydellisen lisätuimen suunnittelu ei ole niin

Yksinkertainen kuin puoli -lisäys.

|

|

Looginen ilmaisu

|

Looginen lauseke puoliainille on:

S = a⊕b;C = a*b.

|

Looginen ilmaisu täyden lisäaineen on:

S = a⊕b⊕cin;Culkona= (a*b)+(csisä-*(a⊕b)).

|

|

Logiikkaportit

|

Se koostuu yhdestä entisestä portista ja yhdestä ja yhdestä ja

portti.

|

Se koostuu kahdesta entisestä tai kahdesta ja portista,

ja yksi tai portti.

|

|

Sovellukset

|

Sitä käytetään laskimissa, tietokoneissa,

Digitaaliset mittauslaitteet jne.

|

Sitä käytetään useissa bittisissä lisäyksissä,

digitaaliset prosessorit jne.

|

|

Vaihtoehtoinen nimi

|

Puolelle ei ole vaihtoehtoista nimeä

Adder.

|

Täysin lisäys tunnetaan myös aaltoileviksi

Adder.

|

Kartoittaa

1: Ero puolisoderin ja täyden lisäaineen välillä

Täydellisen lisäaineen totuustaulukko on avain sen operatiivisen logiikan ymmärtämiseen, jossa kerrotaan tarkan suhteen binaarisyöttöyhdistelmien ja vastaavien tulosten välillä.Tämä taulukko osoittaa kaikki mahdolliset syöttöskenaariot ja niiden tulokset, mikä tekee siitä välttämättömän työkalun digitaalisten logiikkapiirien suunnittelussa ja todentamisessa.Koko lisäys käsittelee kolme tuloa: a, b ja a ja cin (cin), joista kukin voi olla joko 0 tai 1. Tämä johtaa kahdeksan mahdolliseen tuloyhdistelmään.

Jokaiselle näistä yhdistelmistä täyden lisäaineen lähdöt sisältävät summan (summa) ja suorituksen (cout).Summa on kolmen tuloksen modulo-2-lisäys (XOR-operaatio)-A, B ja CIN.Käyttöönotto tapahtuu, kun ainakin kaksi syöttöbittiä on 1. Tämä heijastaa täyden lisäaineen kykyä käsitellä siirtotason peräkkäisissä lisäysoperaatioissa, varmistaen tarkkuuden korkeamman bittisten laskelmissa.

Tarkastellaan, harkitse syöttöskenaariota, jossa kaikki tulot ovat 0 (a = 0, b = 0, c-in = 0).Lähtösumma on 0, ja kanto on myös 0, mikä osoittaa, että hallinnassa ei ole ylimääräistä summaa tai kantoa.Jos vain yksi syöttöbitti on 1, kuten a = 1, b = 0, c-in = 0, lähtösumma on 1 ilman kantoa, mikä osoittaa, että kantoa ei tarvitse siirtää korkeampaan bittiin.Kun kaksi syöttöbittiä ovat 1, kuten a = 1, b = 1, c-in = 0, lähtösumma on 0 (koska 1+1 on 2 on binaarissa ja modulo-2 johtaa 0), mutta kantoOut on 1, mikä osoittaa kuljetuksen, joka on siirrettävä seuraavalle korkeammalle bille.Monimutkaisin skenaario tapahtuu, kun kaikki kolme syöttöbittiä ovat 1 (a = 1, b = 1, c-in = 1);Lähtösumma on 1, ja suoritetaan 1, mikä viittaa siihen, että kantohoito voidaan tarvita myös vielä suuremmilla bitteillä.

|

Eräs

|

B -

|

Csisä-

|

S

|

Culkona

|

|

0 -

|

0 -

|

0 -

|

0 -

|

0 -

|

|

0 -

|

0 -

|

1

|

1

|

0 -

|

|

0 -

|

1

|

0 -

|

1

|

0 -

|

|

0 -

|

1

|

1

|

0 -

|

1

|

|

1

|

0 -

|

0 -

|

1

|

0 -

|

|

1

|

0 -

|

1

|

0 -

|

1

|

|

1

|

1

|

0 -

|

0 -

|

1

|

|

1

|

1

|

1

|

1

|

1

|

Kaavio 2: Täysin Adder -totuustaulukko

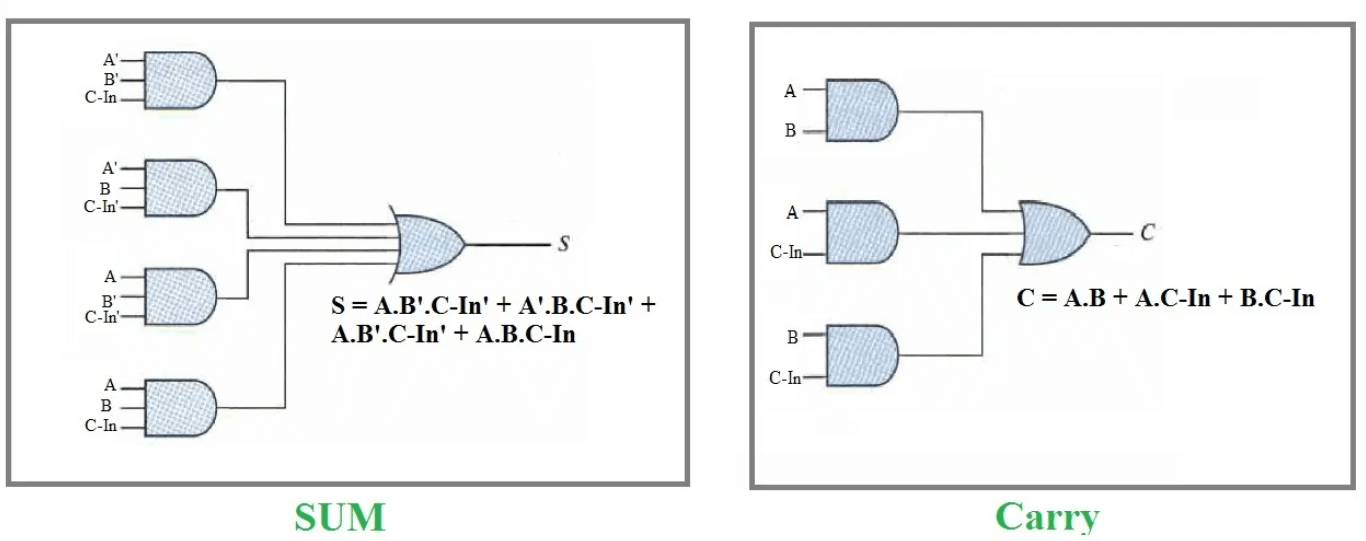

Koko lisätuimen ymmärtäminen käsittää sen toiminnallisuuden leikkaamisen totuustaulukon avulla, jossa syöttöarvojen A, B ja C-In -yhdistelmien eri yhdistelmät johtavat tuotoksiin summa ja cout.Operaation tarttumiseksi yksinkertaistamme logiikkayhtälöitä askel askeleelta.

Logiikan lauseke summalle

Yhtälö alkaa erillisillä tapauksilla, joissa summa on 1:

• 'B' CIN + A 'B CIN' + A B 'CIN' + AB CINA

Tämä yhtälö voidaan tiivistää ryhmittelemällä termejä CIN: n kanssa:

• CIN ('B' + AB) + CIN '(A' B + A B ')

Tämä yksinkertaistaminen johtaa helpompaan toteuttamiseen:

• CIN XOR (A XOR B)

Tämä esitys osoittaa, että summatulos on olennaisesti XOR -operaatio A, B ja CIN: n keskuudessa, joka kaappaa binaarisen lisäyksen ydinkäyttäytymisen, jossa SUM -vaihdot parittoman määrän perusteella.

Cout -logiikka

Alkaen olosuhteista, joissa kanto syntyy:

• A 'b cin + a b' cin + ab c-in ' + ab cin

Yhtälön yksinkertaistaminen, tunnistamme termit, joihin yleensä liittyy kuljetuksen luominen:

• ab + b cin + a

Etsitkö toista menetelmää Cout: n toteuttamiseksi, yhtälö voidaan organisoida uudelleen:

• AB + A CIN + B C-In (A + A ')

Tämä laajenee ja yhdistää yhdistämään kaikki skenaariot, joissa ainakin kaksi panosta on 1:

• ab cin + ab + a c-in + a 'b cin

• ab (1 + cin) + a c-in + a 'b elokuvateatteri

• ab + a c-in (b + b ') + a' b elokuvateatteri

• ab + a b 'cin + a' b -elokuva

• AB + CIN (A 'B + A B')

Lopullinen kompakti lomake cout:

• AB + CIN (A XOR B)

Tämä suoritusyhtälön versio osoittaa, kuinka Cout tuotetaan joko, kun sekä A että B ovat 1 tai kun yksi A tai B on 1 yhdessä A: n kanssa, kapseloi siten logiikan, jota tarvitaan kuljetuksen etenemiseen monissaBit binaarinen lisäys.Tämä virtaviivainen logiikka on erityisen hyödyllinen tehokkaiden digitaalisten piirien toteuttamisessa.

Kuva 4: Koko lisäysyhtälöt

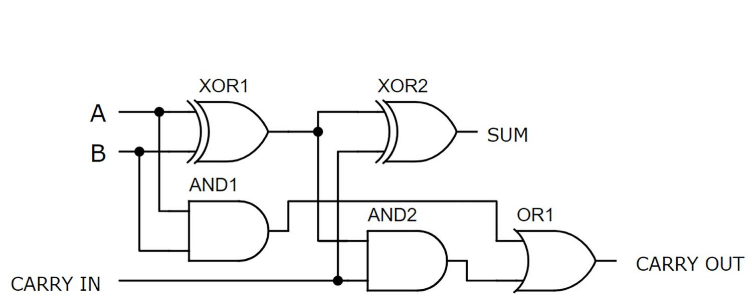

Täydellisen lisäainpiirin toteuttaminen sisältää huolellisesti kahden puolikerroksen ja tai portin kokoamisen laitteen luomiseksi, joka pystyy käsittelemään tehokkaasti kolmen yhden bittisen binaaritulon lisäämistä.Tämä järjestely optimoi piirin monimutkaisuuden ja varmistaa sekä tehokkaan että tarkan laskelman.

Ensimmäisen puoliajan adder ottaa aloittaen kaksi ensisijaista binaarisyötettä, A ja B, jotka ovat lisänumeroita lisättäväksi.Sen keskeinen tehtävä on laskea näiden kahden numeron summa ja alkuperäinen kuljetus.Ensimmäisen puoliajan Adder tuottaa kaksi tulosta: alkuperäinen summa (SUM1) ja alkuperäinen kanto (kanto1).SUM1 on johdettu A: n ja B: n XOR -toiminnasta, mikä osoittaa, onko kokonaismäärällä pariton määrä 1.Carry1, A: n ja B: n välisen operaation tulos, osoittaa, ovatko molemmat numerot 1, edellyttäen kuljetusta seuraavaan korkeampaan bittiin.

Seuraavaksi toisen puoliajan lisäys liittyy prosessiin.Se käyttää SUM-lähtöä sum1 ja kolmannen tulo CIN (kuljetus edellisestä laskelmasta) sen tuloina.Toisen puoliajan lisäys tuottaa kaksi lähtöä: lopullinen summa tulos (SUM2) ja toissijainen kanto (kanto2).SUM2, joka on SUM1: n ja CIN: n XOR -tulos, edustaa kolmen tuloksen lopullista summaa, joka näyttää aggregoituneen binaarisen lisäyksen.Carry2, joka on syntynyt SUM1: n ja CIN: n välillä ja toiminnasta, osoittaa näiden komponenttien tuottaman kantolaitteen.

Kuva 5: Täysin lisäyspiiri kahdella puoliskolla

Lopuksi, täydennyskoulutuksen suorittamiseksi, kantolähtöjen suorittamiseksi ja kanto-2: n käsittelemiseksi tai portti vaaditaan molempien puoliskojen lisäyksistä.Tämä tai portti varmistaa, että kaikki laskelmien aikana tuotetut kuljetukset välitetään oikein lopulliseen lähtöön.Siksi täyden Adderin viimeinen kantolähtö (Cout) on kanto- ja kanto2: n ja kanto2: n tulos.Tämän tai portin sisällyttäminen takaa, että kaikki potentiaaliset kuljetukset lasketaan tarkasti ja välitetään seuraavalle tasolle monimuotoisissa lisäysoperaatioissa varmistaen aritmeettisen toiminnan eheyden useiden bittien välillä.

Täydellisillä lisäyksillä on välttämätön rooli digitaalisessa logiikan suunnittelussa, joka tarjoaa lukuisia etuja, jotka tekevät niistä välttämättömiä erilaisissa tietojenkäsittely- ja tietojenkäsittelyskenaarioissa.Heidän ensisijaisiin etuihinsa kuuluvat huomattava joustavuus, nopeakäsittelynopeudet ja tehokas kantohoito.Nämä piirteet tekevät täydellisistä lisäyksistä, jotka ovat ihanteellisia monimutkaisten aritmeettisten toimintojen ja logiikkatoimintojen suorittamiseen, etenkin sovelluksissa, jotka vaativat peräkkäistä monimuotoista lisäystä.

Edut

Joustavuus: Täydelliset lisälaitteet ovat erinomaisia kyvyssä käsitellä useita binaarisia tuloja (A, B ja CIN) samanaikaisesti.Niitä voidaan myös laajentaa suurempiin lisäystaulukkoihin käsittelemään pidempiä binaarilukuja.Tämä skaalautuvuus on tärkeä korkean suorituskyvyn aritmeettisten logiikkayksiköiden (ALUS) rakentamiselle, jonka on suoritettava monimutkaisia mon-bittisiä aritmeettisia ja logiikkatoimintoja.

Nopeus: Heidän sisäisen rinnakkaisprosessointiarkkitehtuurinsa ansiosta täydet lisäosat voivat suorittaa kaikkien tulon lisäämisen yhdessä kellosyklissä ja määrittää samalla myös lähtöjä.Tämä kyky tukee jatkuvia lisäystoimintoja ja on välttämätöntä reaaliaikaisessa tietojenkäsittelyssä nykyaikaisissa mikroprosessoreilla ja nopealla laskentalaitteella.

Haitat

Täydelliset lisälaitteet ovat kuitenkin myös merkittäviä haittoja:

Suunnittelun ja toteutuksen monimutkaisuus: Täydelliset lisäosat sisältävät useita logiikkaportteja ja monitasoisia kantolaitteita, mikä tekee niiden suunnittelukompleksista.Tämä monimutkaisuus ei vain lisää valmistuskustannuksia, vaan voi myös vaikuttaa piirien luotettavuuteen.

Levitysviiveongelmat: Kannata etenemistä voi kulkea useiden logiikkaporttien läpi, joista kukin lisää viivettään.Tämä voi rajoittaa yleistä laskennallista nopeutta laajamittaisten toimintojen aikana, etenkin laajoissa tietokonejärjestelmissä ja erittäin laajan mittakaavan integraation (VLSI) ja nopean prosessorien suunnittelussa.Viivästyksestä voi tulla merkittävä pullonkaula suorituskyvyssä.

Näiden ongelmien lieventämiseksi insinöörit tutkivat jatkuvasti tehokkaampia piirimalleja.Strategioita ovat nopeamman logiikan porttitekniikan käyttäminen, piirijärjestelmien optimointi polun pituuksien lyhentämiseksi ja edistyneiden tekniikoiden, kuten kuljetussäästöaineiden, kehittäminen viivästymisen vähentämiseksi kuljetusten etenemisessä.

Täydellisiä lisäosia käytetään laajasti digitaalisessa logiikassa, joka on arvostettu niiden joustavuuteen ja tehokkuuteen, mikä tekee niistä keskeisiä monien tietojenkäsittely- ja tietojenkäsittelytehtävien suhteen.Niiden sovellus ulottuu aritmeettisten perustoimintojen suhteen monimutkaiseen signaalinkäsittelyyn ja järjestelmän hallintaan.Tässä on yksityiskohtainen katsaus joihinkin avainalueisiin, joilla täydet lisäosat ovat olennaisia.

Aritmeettiset piirit

Yksi täyden lisäaineiden suoraviivaisimmista käytöstä on aritmeettisissa piireissä, joissa ne suorittavat binaarista lisäystä.Erityisen ratkaisevan tärkeätä monen bittisen numeron lisäyksessä täydet lisäosat hallitsevat pidempiä binaarisekvenssejä CSS: n avulla.Tässä järjestelyssä jokainen täyden adder käsittelee lisäyksen bittisovelluksestaan ja kantolaitteesta alemmasta bitistä ja siirtää sitten uuden kanteen seuraavaan korkeamman bitin täyteen lisäaineen.Tämä kaskadi mahdollistaa kattavan moni-bittisen lisäyksen koko numeroalueella.

Tietojenkäsittely

Täydellisissä lisäyksissä on myös keskeinen rooli edistyneissä tietojenkäsittelytehtävissä, kuten digitaalisen signaalinkäsittelyn (DSP) suodattamisessa ja Fourier -muunnoksissa, joissa tarvitaan tarkkoja ja nopeaa aritmeettisia operaatioita.Lisäksi tietoturvan alueella, mukaan lukien tietojen salaus- ja virheiden havaitsemis- ja korjausalgoritmit, kuten pariteettitarkistukset ja syklinen redundanssitarkistus (CRC) koodin luominen, täydet lisäosat ovat välttämättömiä välttämättömien bittitoimintojen suorittamiseksi.

Laskuri

Digitaalisissa laskureissa täydet lisäosat ovat välttämättömiä sekä lisäys- että alennustoimintojen toteuttamisessa, etenkin modulaarisissa ja synkronisissa laskureissa.He hallitsevat tarkasti kantokantaja ja lainaa tarkan laskennan varmistamiseksi.

Multiplekserit (MUX) ja demultiplekserit (Demux)

Multipleksereissä ja demultipleksereissä täydet lisälaitteet ovat kriittinen rooli kanavan valinnassa ja tiedon jakautumisessa.He osallistuvat logiikkaan, joka määrittää, mitä kanavia käytetään datan syöttämiseen ja ulostulossa, tekemällä päätöksiä logiikan ohjaussignaalien perusteella.

Muistitekniikka

Muistiosoitteessa täydet lisäosat auttavat luomaan osoitekignaaleja muistin sijaintien dynaamiseen pääsyyn.Tämä on erityisen tärkeää dynaamisessa satunnais-pääsyn muistissa (DRAM) ja muissa tallennusjärjestelmissä, joissa täydet lisäosat tukevat kompleksisia osoitekaskelmia muisti-pääsyn tehokkuuden parantamiseksi.

Aritmeettiset logiikkayksiköt (ALU)

Lopuksi, koska mikroprosessorien ja digitaalisten signaaliprosessorien aritmeettisten logiikkayksiköiden peruskomponentit ovat tärkeitä.ALU käsittelee kaikkia aritmeettisia ja logiikkatoimintoja, joissa täydet lisäosat varmistavat, että tiedot käsitellään sekä nopeasti että tarkasti.

Täydelliset lisäosat voidaan rakentaa käyttämällä erilaisia logiikkaportteja ja kokoonpanoja.Täällä tutkimme neljää erilaista toteutusta korostamalla niiden asennus- ja operatiivisia vivahteita.

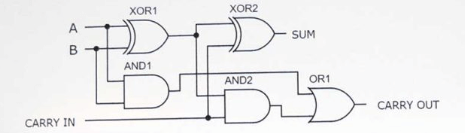

Koko lisäys rakennettu XOR: lla, ja tai porteilla

Kuva 6: XOR: lla rakennetun täyden lisätuorin ja tai / / logiikan portit

Tämä esimerkki esittelee leipälevylle rakennetun täydellisen lisäaineen erillisillä transistoreilla.Kokoonpano käsittää viisi logiikkaporttia: kaksi XOR -porttia, kaksi ja portti ja yksi tai portti, mikä vaatii yhteensä 21 transistoria.Tulot A ja B on kytketty leipälevyn vasempaan yläkulmaan, ja ne saavat A +5 V: n.Näitä tuloja ohjataan kahdella kytkentäkytkimellä.Kaksi vasemmassa yläkulmassa olevaa LEDiä osoittavat tulojen A ja B tilat, kun taas kaksi oikealla puolella olevaa LEDiä näyttää lähtöt.Piirissä käytetyt vastukset ovat kaikki 2,2 000 ohmia.Kun tulot A ja B ovat päällä ja kuljetus on pois päältä, lähtö näyttää binaarisen arvon 10, mikä edustaa summaa 2 (1 + 1 + 0 = 10).Ensimmäisellä 12 transistorilla rakennettu XOR-portit käsittelevät ensisijaista summausta, kun taas leipälevyn alaosa sisältää ja / / portit kantotoimenpiteisiin, värikoodattu johdotus parantaa selkeyttä ja vianetsintä.

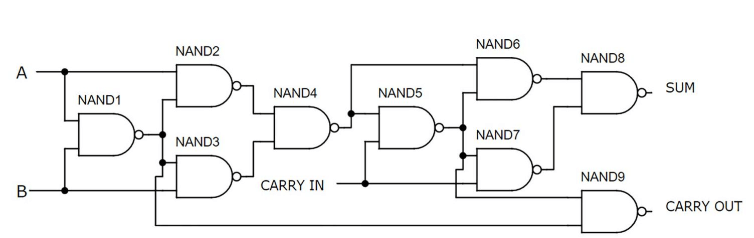

Täysin lisäys Nand Gates -sovelluksella

Kuva 7: Koko lisäys Nand Gates -sovelluksella

Tämä täysi lisäin käyttää yhdeksää NAND -porttia, ja jokainen portti on valmistettu kahdesta transistorista, yhteensä 18 transistoria.Tämä menetelmä on yksi yksinkertaisimmista ja tehokkaimmista tavoista rakentaa täydellinen lisäin erillisiä komponentteja käyttämällä.Kaikki portit on koottu leipälevyn yläosaan, kun taas kytkimet miehittävät alaosan.Piirin toiminnallisuus osoitetaan tuloilla A ja B on ja siirto

Täysin lisäys Nortes

Kuva 8: Täysi lisäys Nortes -palvelun kanssa

Yhdeksän Nort -portilla rakennettu, kukin vaatii kahta transistoria, tämä asennus käyttää myös yhteensä 18 transistoria.Täydellisen lisäaineen rakentaminen NORES: n kanssa tarjoaa hyvän vaihtoehdon, mutta siihen liittyy monimutkaisempi johdotus verrattuna NAND -porteihin.Jokainen NOR -porttien transistori on maadoitettu, kun keräilijät on kytketty oranssilla hyppyjohdolla siisti ja järjestäytyneen johdotuksen varmistamiseksi.Tämä konfiguraatio on esitetty sisääntuloilla A ja B aktivoituna ja kantoratkaisu deaktivoituna, mikä johtaa lähtöihin, joissa kuljetus on aktiivinen ja summa on pois päältä.

Koko tämän Adder -tekniikan etsinnän ajan, puoliksi lisäaineista hienostuneisiin täyteen lisäysmalliin, on selvää, että nämä komponentit ovat perustana digitaalisen elektroniikan edistymiselle.Toimintaominaisuudet ja toteutusesimerkit korostavat lisäaineiden monipuolisuutta ja tehokkuutta erilaisissa laskennallisissa asetuksissa.Tutkimalla lisäaineiden rakennetta ja toimintaa, etenkin niiden totuustaulukoiden ja ominaisyhtälöiden kautta, saamme arvokkaita näkemyksiä niiden ominaisuuksista ja rajoituksista.Tämä tieto on tärkeä tekijä tehokkaampien ja nopeampien tietojenkäsittelyjärjestelmien suunnittelun edistämisessä.Viime kädessä Adders ei vain yksinkertaista monimutkaisia binaarilaskelmia, vaan mahdollistaa myös tekniikan lisääntymisen niin monimuotoisilla alueilla kuin tietojenkäsittely, muistin allokointi ja digitaalinen signaalinkäsittely.Digitaalitekniikan kehittyessä meneillään oleva hienostuneisuus ja innovaatio Adder -suunnittelussa ovat edelleen kulmakivi edistyneempien laskennallisten arkkitehtuurien kehittämisessä varmistaen, että nämä peruskomponentit pysyvät digitaalisen järjestelmän suunnittelun ja toteutuksen ytimessä.

Usein kysyttyjä kysymyksiä [UKK]

1. Mikä on täydellinen lisäyspiiri?

Täysin lisäys on digitaalinen piiri, joka lisää kolme binaarista bittiä summan ja kantolähteen tuottamiseksi.Se on suunniteltu käsittelemään kolmen tuloksen lisäämistä: kaksi merkittävää bittiä ja yksi kuljetusbitti edellisestä lisäyksestä.Tämä mahdollistaa sen käytön peräkkäisissä vaiheissa monien binaarien lukujen lisäämiseksi.

2. Kuinka monta ja, tai xor täydessä lisäyksessä?

Tyypillinen täysi lisäin sisältää:

Kaksi Xor -porttia summan luomiseksi.

Kaksi ja portit osallistumaan suorituksen laskelmaan.

Yksi tai portti suoritettavan tuloksen viimeistelemiseksi.

3. Mikä on kuljetustulo täydessä lisäyksessä?

Kantotulo (CIN) täydessä lisäyksessä on kantobitti aikaisemman alemman merkittävien bittien lisäämisestä mon-bittisessä binaarisessa lisäyksessä.Sen avulla koko lisäys voi harkita tätä edellistä kantoa laskettaessa nykyistä summaa ja uutta suoritusta.

4. Miksi käyttää täydellistä lisäystä puolikkaan lisäysten sijasta?

Koko lisäystä käytetään puolikerroksen sijasta, koska se voi lisätä kolme bittiä (mukaan lukien aikaisempien lisäysten kuljetus), joten se sopii ketjuttamiseen yhdessä monien bittisten numeroiden lisäämiseksi.Puoli-syöttö voi lisätä vain kaksi bittiä, eikä sillä ole varausta kuljetukselle, mikä rajoittaa sen käyttöä binaarisen lisäyksen yksinkertaisimpiin muotoihin ilman peräkkäistä kuljetusta.