# High-Speed Microcontroller User's Guide: DS80C390 Supplement

This document is provided as a supplement to the *High-Speed Microcontroller User's Guide*, covering new or modified features specific to the DS80C390. *This document must be used in conjunction with Dallas Semiconductor's* **High-Speed Microcontroller User's Guide**. Addenda are arranged by the section numbers that correspond to sections in the *High-Speed Microcontroller User's Guide*.

The following additions and changes, with respect to the *High-Speed Microcontroller User's Guide*, are contained in this document. This document is a work in progress, and updates/additions are added when available.

#### **TABLE OF CONTENTS**

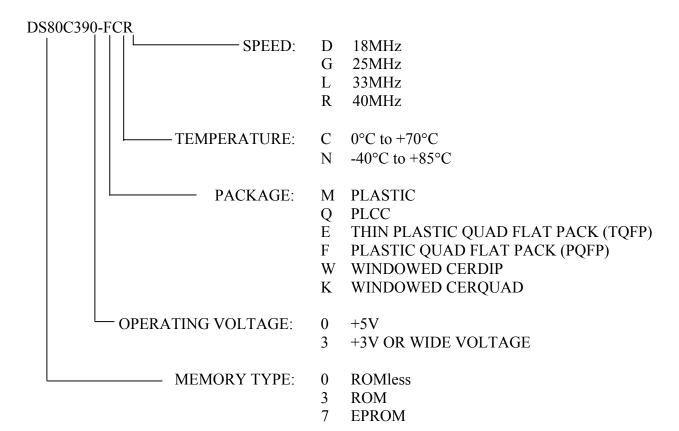

| 4 | ADDENDUM TO SECTION 2: ORDERING INFORMATION                | 5  |

|---|------------------------------------------------------------|----|

| 4 | ADDENDUM TO SECTION 4: PROGRAMMING MODEL                   | 6  |

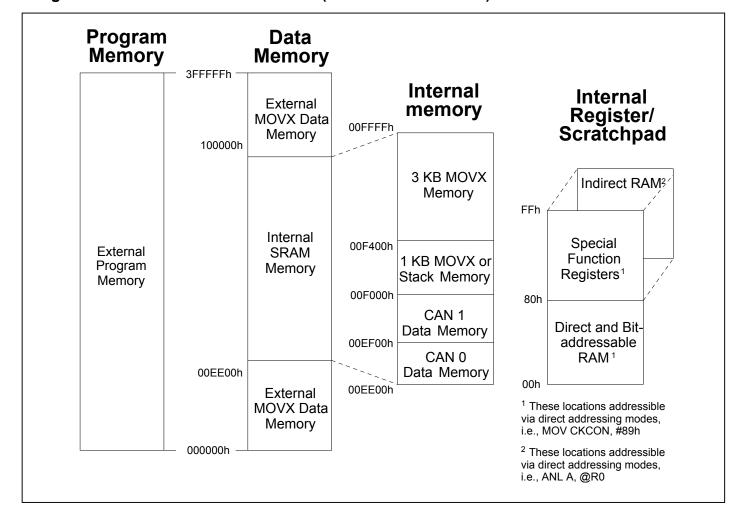

|   | MEMORY MAP                                                 |    |

|   | REGISTER MAP                                               |    |

|   | BIT ADDRESSABLE LOCATIONS                                  |    |

|   | Working Registers                                          |    |

|   | STACK                                                      |    |

|   | SPECIAL FUNCTION REGISTERS.                                |    |

|   | PORT 4 (P4)                                                |    |

|   | STACK POINTER (SP)                                         |    |

|   | DATA POINTER LOW 0 (DPL)                                   |    |

|   | DATA POINTER HIGH 0 (DPH)                                  |    |

|   | DATA POINTER LOW 1 (DPL1)                                  |    |

|   | DATA POINTER HIGH 1 (DPH1)                                 |    |

|   | DATA POINTER SELECT (DPS)                                  |    |

|   | POWER CONTROL (PCON)                                       |    |

|   | TIMER/COUNTER CONTROL (TCON)                               |    |

|   | TIMER MODE CONTROL (TMOD)                                  |    |

|   | TIMER 0 LSB (TL0)                                          |    |

|   | TIMER 1 LSB (TL1)                                          |    |

|   | TIMER 0 MSB (TH0)                                          |    |

|   | TIMER 1 MSB (TH1)                                          |    |

|   | CLOCK CONTROL (CKCON)                                      |    |

|   | PORT 1 (P1)                                                |    |

|   | EXTERNAL INTERRUPT FLAG (EXIF)                             |    |

|   | PORT 4 CONTROL REGISTER (P4CNT)                            | 24 |

|   | DATA POINTER EXTENDED REGISTER 0 (DPX)                     | 25 |

|   | DATA POINTER EXTENDED REGISTER 1 (DPX1)                    | 25 |

|   | CAN 0 RECEIVE MESSAGE STORED REGISTER 0 (CORMSO)           |    |

|   | CAN 0 RECEIVE MESSAGE STORED REGISTER 1 (CORMS1)           | 27 |

|   | SERIAL PORT 0 CONTROL (SCON0)                              |    |

|   | SERIAL DATA BUFFER 0 (SBUF0)                               | 29 |

|   | REVISION ID REGISTER (RID)                                 | 29 |

|   | EXTENDED STACK POINTER REGISTER (ESP)                      | 30 |

|   | ADDRESS PAGE REGISTER (AP)                                 | 30 |

|   | ADDRESS CONTROL REGISTER (ACON)                            | 31 |

|   | CAN 0 Transmit Message Acknowledgement Register 0 (C0TMA0) | 32 |

|   | CAN 0 TRANSMIT MESSAGE ACKNOWLEDGEMENT REGISTER 1 (COTMA1) | 33 |

|   | PORT 2 (P2)                                                |    |

|   | PORT 5 (P5)                                                | 34 |

|   |                                                            |    |

| Port 5 Control Register (P5CNT)                            |          |

|------------------------------------------------------------|----------|

| CAN 0 CONTROL REGISTER (C0C)                               |          |

| CAN 0 STATUS REGISTER (COS)                                |          |

| CAN 0 Interrupt Register (COIR)                            | 42       |

| CAN 0 Transmit Error Register (C0TE)                       | 43       |

| CAN 0 Receive Error Register (CORE)                        | 44       |

| INTERRUPT ENABLE (IE)                                      |          |

| SLAVE ADDRESS REGISTER 0 (SADDR0)                          | 45       |

| SLAVE ADDRESS REGISTER 1 (SADDR1)                          | 45       |

| CAN 0 Message Center 1 Control Register (C0M1C)            | 46       |

| CAN 0 Message Center 2 Control Register (C0M2C)            |          |

| CAN 0 Message Center 3 Control Register (C0M3C)            |          |

| CAN 0 Message Center 4 Control Register (C0M4C)            |          |

| CAN 0 Message Center 5 Control Register (C0M5C)            |          |

| Port 3 (P3)                                                |          |

| CAN 0 Message Center 6 Control Register (C0M6C)            | 51       |

| CAN 0 Message Center 7 Control Register (C0M7C)            |          |

| CAN 0 Message Center 8 Control Register (C0M8C)            |          |

| CAN 0 Message Center 9 Control Register (C0M9C)            |          |

| CAN 0 Message Center 10 Control Register (C0M10C)          |          |

| INTERRUPT PRIORITY (IP)                                    |          |

| SLAVE ADDRESS MASK ENABLE REGISTER 0 (SADENO)              |          |

| SLAVE ADDRESS MASK ENABLE REGISTER 1 (SADEN1)              |          |

| CAN 0 Message Center 11 Control Register (C0M11C)          |          |

| CAN 0 Message Center 12 Control Register (C0M12C)          |          |

| CAN 0 Message Center 13 Control Register (C0M13C)          |          |

| CAN 0 Message Center 14 Control Register (C0M14C)          |          |

| CAN 0 Message Center 15 Control Register (C0M15C)          | 55       |

| SERIAL PORT CONTROL (SCON1)                                | 55       |

| SERIAL DATA BUFFER 1 (SBUF1)                               |          |

| Power Management Register (PMR)                            | 57       |

| STATUS REGISTER (STATUS)                                   |          |

| MEMORY CONTROL REGISTER (MCON)                             | 59       |

| TIMED ACCESS REGISTER (TA)                                 |          |

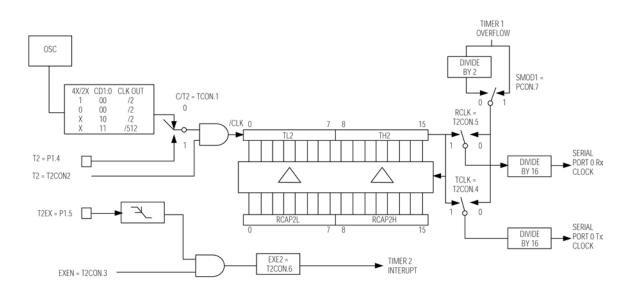

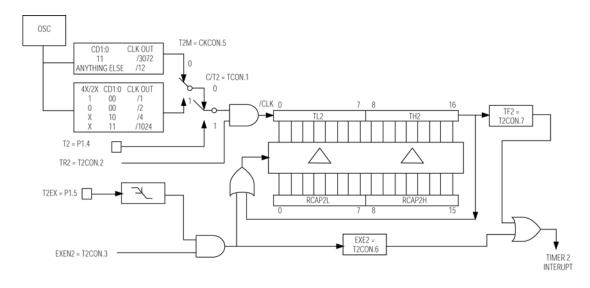

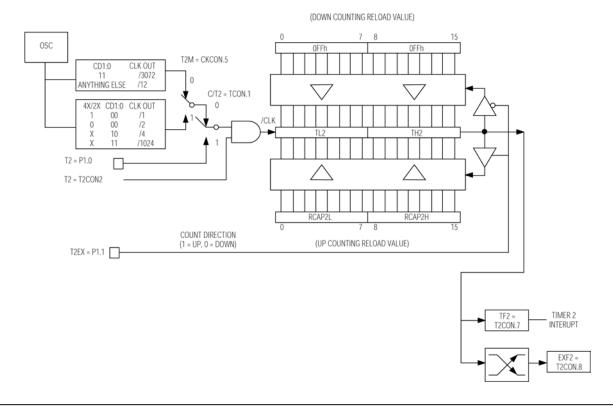

| TIMER 2 CONTROL (T2CON)                                    |          |

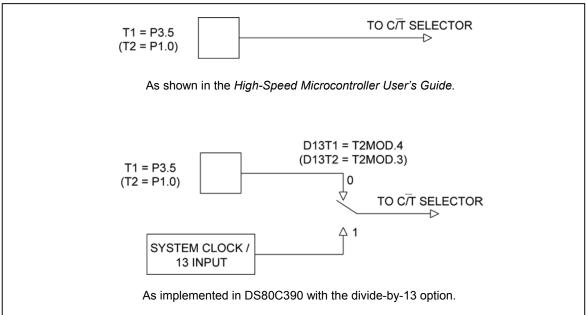

| TIMER 2 MODE (T2MOD)                                       |          |

| TIMER 2 CAPTURE LSB (RCAP2L)                               |          |

| TIMER 2 CAPTURE MSB (RCAP2H)                               |          |

| TIMER 2 LSB (TL2)                                          |          |

| TIMER 2 MSB (TH2)                                          |          |

| CLOCK OUTPUT REGISTER (COR)                                | 64       |

| PROGRAM STATUS WORD (PSW)                                  |          |

| MULTIPLIER CONTROL REGISTER ZERO (MCNT0)                   | 66       |

| MULTIPLIER CONTROL REGISTER ONE (MCNT1)                    | 67       |

| MULTIPLIER A REGISTER (MA)                                 |          |

| MULTIPLIER B REGISTER (B)                                  |          |

| MULTIPLIER C REGISTER (C)                                  |          |

| CAN 1 RECEIVE MESSAGE STORED REGISTER 0 (C1RMS0)           |          |

| CAN 1 Receive Message Stored Register (C1RMS1)             |          |

| WATCHDOG CONTROL (WDCON)                                   |          |

| CAN 1 Transmit Message Acknowledgement Register 0 (C1TMA0) |          |

| CAN 1 TRANSMIT MESSAGE ACKNOWLEDGEMENT REGISTER 0 (C1TMA0) | 12<br>72 |

| ACCUMULATOR (A OR ACC)                                     |          |

| CAN 1 Control Register (C1C)                               |          |

| CAN 1 STATUS REGISTER (C1S)                                |          |

| CAN 1 Interrupt Register (C1IR)                            |          |

| CAN 1 Transmit Error Register (C1TE)                       |          |

| CAN 1 Profive Eppon Projeten (C1DE)                        | 01<br>01 |

| MOVX EXTENDED ADDRESS REGISTER (MXAX).   82 CAN 1 MESSAGE CENTER 1 CONTROL REGISTER (C1M1C).   83 CAN 1 MESSAGE CENTER 2 CONTROL REGISTER (C1M2C).   86 CAN 1 MESSAGE CENTER 3 CONTROL REGISTER (C1M3C).   86 CAN 1 MESSAGE CENTER 3 CONTROL REGISTER (C1M3C).   86 CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M4C).   86 CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M4C).   86 CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M4C).   87 CAN 1 MESSAGE CENTER 7 CONTROL REGISTER (C1M4C).   87 CAN 1 MESSAGE CENTER 7 CONTROL REGISTER (C1M7C).   87 CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M7C).   87 CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M9C).   87 CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M9C).   88 CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M9C).   88 CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M1C).   88 CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M1C).   89 CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M1C).   89 CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M1C).   89 CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M1C).   89 CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M1C).   89 CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M1C).   89 CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M1C).   89 CAN 1 MESSAGE CENTER 16 CONTROL REGISTER (C1M1C).   89 CAN 1 MESSAGE CENTER 16 CONTROL REGISTER (C1M1C).   90 ADDENDUM TO SECTION 5: CPU TIMING   91 SYSTEM CLOCK SELECTION   91 CHANDIAND TO SECTION 5: CPU TIMING   91 SYSTEM CLOCK SELECTION   91 CHANDIAND TO SECTION 6: MEMORY ACCESS   93 EXTERNAL MEMORY INTERFACING   92 ADDENDUM TO SECTION 6: MEMORY ACCESS   93 EXTERNAL MEMORY INTERFACING   93 CAN 1 MESSAGE CENTER 16 CONTROL REGISTER (C1M14C).   90 ADDENDUM TO SECTION 8: RESET CONDITIONS   91 CHANDIAND TO SECTION 8: RESET CONDITIONS   91 CHANDIAND TO SECTION 8: RESET CONDITIONS   91 CHANDIAND TO SECTION 10: PARALLEL I/O   90 CHANDIAND TO SECTION 11: PROGRAMMABLE TIMERS   101 CHANDIAND TO SECTION 12: SERIAL I/O   101 CHADA CLOCK OUTPUT   110 IRDA CLOCK OUTPUT   110 IRDA CLOCK OUTPUT   110 IRDA CLOCK OUTPUT   111 CADDENDUM TO SECTION 13: TIMED ACCE                                                                                                                                                                                                                                       | CAN 1 MESSAGE CENTER 1 CONTROL REGISTER (C1MZC). CAN 1 MESSAGE CENTER 3 CONTROL REGISTER (C1MZC). CAN 1 MESSAGE CENTER 3 CONTROL REGISTER (C1M3C). CAN 1 MESSAGE CENTER 5 CONTROL REGISTER (C1M3C). CAN 1 MESSAGE CENTER 5 CONTROL REGISTER (C1M4C). CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M5C). B REGISTER (B). CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M5C). CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M7C). CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M7C). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M1C). CENTENDED INTERRUPT PRIORITY (EIP). CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M1C). CAN 1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 82                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| CAN 1 MESSAGE CENTER 2 CONTROL REGISTER (C1M2C).  CAN 1 MESSAGE CENTER 3 CONTROL REGISTER (C1M3C).  86 CAN 1 MESSAGE CENTER 4 CONTROL REGISTER (C1M4C).  87 CAN 1 MESSAGE CENTER 5 CONTROL REGISTER (C1M5C).  88 REGISTER (B).  87 CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M5C).  87 CAN 1 MESSAGE CENTER 7 CONTROL REGISTER (C1M5C).  87 CAN 1 MESSAGE CENTER 7 CONTROL REGISTER (C1M6C).  87 CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M6C).  87 CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M6C).  88 CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M9C).  88 CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M9C).  88 CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M9C).  88 CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M1C).  88 CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M1C).  89 CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M1C).  80 CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M1C).  80 CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M1C).  80 CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M1C).  80 CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  90 CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  90 ADDENDUM TO SECTION 5: CPU TIMING  91 CHANCING THE SYSTEM CLOCK MEGISTER (C1M14C).  90 ADDENDUM TO SECTION 5: CPU TIMING  91 SYSTEM CLOCK SELECTION.  91 CHANCING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY.  92 ADDENDUM TO SECTION 6: MEMORY ACCESS  93 EXTERNAL MEMORY INTERFACING  93 USING THE COMBINED CHIP-ENABLE SIGNALS  94 MPILEMENTING A BOOTLOADER USING INTERNAL SRAM  95 EXAMPLE DSBOG399 MEMORY CONFIGURATION  95 ADDENDUM TO SECTION 7: POWER MANAGEMENT  100 POWER ON/FALL RESET  101 WATCHOO'S ETWER CLOCK SURCES  100 ADDENDUM TO SECTION 10: PARALLEL I/O.  104 POWER ON/FALL RESET  101 WATCHOO'S ETWER CLOCK SURCES  100 ADDENDUM TO SECTION 11: PROGRAMMABLE TIMERS  106 DIVIDE-BY-13 OPTION.  110 PROGRAMMABLE CLOCK OUTPUT  111 ADDENDUM TO SECTION 12: SERIAL I/O.  112 ADDENDUM TO SECTION 13: TIMED ACCESS PROTECTION.  113                                                                                                                                                                                                                                                                                                                                                                         | CAN 1 MESSAGE CENTER 2 CONTROL REGISTER (C1MAC). CAN 1 MESSAGE CENTER 3 CONTROL REGISTER (C1MAC). CAN 1 MESSAGE CENTER 4 CONTROL REGISTER (C1MAC). CAN 1 MESSAGE CENTER 5 CONTROL REGISTER (C1MAC). CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1MSC). B REGISTER (B). CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1MC). CAN 1 MESSAGE CENTER 7 CONTROL REGISTER (C1MC). CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1MC). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1MC). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1MGC). CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1MIC). CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1MIC). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1MIC). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1MIC). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1MIC). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1MIC).  CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1MIC).  CAN 1 MESSAGE CENTER 16 CONTROL REGISTER (C1MIC).  CAN 1 MESSAGE CENTER 17 CONTROL REGISTER (C1MIC).  CAN 1 MESSAGE CENTER 18 CONTROL | MOVX EXTENDED ADDRESS REGISTER (MXAX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 82                                                                              |

| CAN 1 MESSAGE CENTER 3 CONTROL REGISTER (C1M3C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CAN 1 MESSAGE CENTER 3 CONTROL REGISTER (C1M3C). CAN 1 MESSAGE CENTER 5 CONTROL REGISTER (C1M5C). B REGISTER (B). CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M5C). B REGISTER (B). CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 7 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M7C). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). ADDENDUM TO SECTION 5: CPU TIMING  SYSTEM CLOCK SELECTION. CHANCING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY.  ADDENDUM TO SECTION 6: MEMORY ACCESS  EXTERNAL MEMORY INTERFACING. USING THE COMBINED CHIP-ENABLE SIGNALS MIPLEMENTING A BOOTLOAGER USING INTERNAL SRAM EXAMPLE DSBOC390 MEMORY CONFIGURATION.  ADDENDUM TO SECTION 7: POWER MANAGEMENT  ADDENDUM TO SECTION 8: RESET CONDITIONS  11 POWER MANAGEMENT MODES  SWITCHING BETWEEN CLOCK SOURCES.  12 ADDENDUM TO SECTION 8: RESET CONDITIONS  11 POWER MANAGEMENT MODES  SWITCHING BETWEEN CLOCK SOURCES.  12 ADDENDUM TO SECTION 10: PARALLEL I/O.  14 PORT 1 PORTS 4 AND 5.  0 CUTPUT FUNCTIONS  17 PORTS 4 AND 5.  18 PORT 1 PORTS 4 AND 5.  19 PORT 1 PORTS 4 AND 5.  10 PORT 1 PORTS 4 AND 5.  11 PORTS 4 AND 5.  12 PORT 1 PORTS 4 AND 5.  13 PORDENDUM TO SECTION 12: SERIAL I/O.  14 PORTS 4 AND 5.  15 PORT 4 BOOTLON 5 CONTROL 5 CONT | CAN 1 Message Center 1 Control Register (C1M1C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83                                                                              |

| CAN 1 MESSAGE CENTER 4 CONTROL REGISTER (C1M4C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CAN 1 MESSAGE CENTER 4 CONTROL REGISTER (C1M4C). CAN 1 MESSAGE CENTER 5 CONTROL REGISTER (C1M5C). B REGISTER (B). CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M5C). CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M10C). EXTENDED INTERRUPT PROTROLY (EIP). CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M11C). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M11C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M11C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). ADDENDUM TO SECTION 5: CPU TIMING. SYSTEM CLOCK SELECTION. CHANGING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY. ADDENDUM TO SECTION 6: MEMORY ACCESS. EXTERNAL MEMORY INTERFACING. USING THE COMBINED CHIP-ENABLE SIGNAL SHALL  | CAN 1 Message Center 2 Control Register (C1M2C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 86                                                                              |

| CAN 1 MESSAGE CENTER 5 CONTROL REGISTER (C1M5C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CAN 1 MESSAGE CENTER 5 CONTROL REGISTER (C1M5C).  B REGISTER (B).  CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M6C).  CAN 1 MESSAGE CENTER 7 CONTROL REGISTER (C1M7C).  CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M7C).  CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M6C).  CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M9C).  CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M10C).  EXTENDED INTERRUPT PRIORITY (EIP).  CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M11C).  CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M12C).  CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M13C).  CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M13C).  CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  ADDENDUM TO SECTION 5: CPU TIMING  SYSTEM CLOCK SELECTION.  CHANGING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY.  ADDENDUM TO SECTION 6: MEMORY ACCESS  EXTERNAL MEMORY INTERFACING.  USING THE COMBINEO CHP-ENABLE SIGNALS.  IMPLEMENTING A BOOTLOADER USING INTERNAL SRAM  EXAMPLE DS80C390 MEMORY CONFIGURATION.  ADDENDUM TO SECTION 7: POWER MANAGEMENT  ADDENDUM TO SECTION 8: RESET CONDITIONS.  11 POWER MANAGEMENT MODES.  SWITCHING BETWEEN CLOCK SOURCES.  12 ADDENDUM TO SECTION 8: RESET CONDITIONS.  14 EXTERNAL RESET.  15 EXTERNAL RESET.  16 EXTERNAL RESET.  17 WATCHOOS TIMER RESET.  18 EXTERNAL RESET.  19 POWER MANAGEMENT MODES.  10 POWER STATE.  11 PORTS A AND 5.  11 PORTS A AND 5.  12 OUTPUT FUNCTIONS.  11 PORTS A AND 5.  12 OUTPUT FUNCTIONS.  13 ADDENDUM TO SECTION 11: PROGRAMMABLE TIMERS.  14 DENDUM TO SECTION 11: PROGRAMMABLE TIMERS.  15 OUTPUT FUNCTIONS.  16 BDT (805 I STANDARD) ADDRESSING MODE.  16 BDT (805 I STANDARD) ADDRESSING MODE.  16 BDT (805 I STANDARD) ADDRESSING MODE.                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |

| B REGISTER (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | B REGISTER (B). CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1MFC). CAN 1 MESSAGE CENTER 7 CONTROL REGISTER (C1MFC). CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1MFC). CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1MBC). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1MBC). CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1MBC). CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1MDC). CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M1C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  ADDENDUM TO SECTION 5: CPU TIMING SYSTEM CLOCK SELECTION. CHANGING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY.  ADDENDUM TO SECTION 6: MEMORY ACCESS EXTERNAL MEMORY INTERFACING. USING THE COMBINEO CHIP-ENABLE SIGNALS. MIPLEMENTING A BOOTLOADER USING INTERNAL SRAM EXAMPLE DS80C390 MEMORY CONFIGURATION.  ADDENDUM TO SECTION 7: POWER MANAGEMENT.  11  POWER MANAGEMENT MODES SWITCHING BETWEEN CLOCK SOURCES. 11  ADDENDUM TO SECTION 8: RESET CONDITIONS 11  RESET SOURCES 10  11  POWER MANAGEMENT MODES 11  RESET SOURCES 11  12  13  14  15  15  16  17  17  18  17  18  18  19  19  17  19  19  17  19  19  10  10  11  11  11  11  12  11  12  13  14  15  15  16  17  16  17  17  17  18  18  19  19  10  10  10  11  11  11  11  11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |

| CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M7C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CAN 1 MESSAGE CENTER 6 CONTROL REGISTER (C1M6C). CAN 1 MESSAGE CENTER 7 CONTROL REGISTER (C1M7C). CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M8C). CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M8C). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M9C). CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M10C). EXTENDED INTERRUPT PRIORITY (EIP). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M11C). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). ADDENDUM TO SECTION 5: CPU TIMING SYSTEM CLOCK SELECTION CHARGING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY  ADDENDUM TO SECTION 6: MEMORY ACCESS EXTERNAL MEMORY INTERFACING. USING THE COMBINED CHIP-ENABLE SIGNALS. IMPLEMENTING A BOOTLOADER USING INTERNAL SRAM EXAMPLE DSBOC390 MEMORY CONTRIGURATION.  ADDENDUM TO SECTION 7: POWER MANAGEMENT.  11 POWER MANAGEMENT MODES. 15 ADDENDUM TO SECTION 8: RESET CONDITIONS. 11 RESET SOURCES. 15 POWER-COMPAIL RESET. 11 WATCHDOG TIMER RESET. 11 WATCHDOG TIMER RESET. 11 WATCHDOG TIMER RESET. 11 WATCHDOG TIMER RESET. 11 N-SYSTEM DISABLE MODE. 11 ADDENDUM TO SECTION 11: PROGRAMMABLE TIMERS. 11 DIVIDE-BY-13 OPTION. 11 PORTS 4 AND 5. 00 UTPUT FUNCTIONS. 11 ADDENDUM TO SECTION 12: SERIAL I/O. 11 ADDENDUM TO SECTION 13: SERIAL I/O. 11 ADDENDUM TO SECTION 11: PROGRAMMABLE TIMERS. 11 BOUND OF THE PROGRAMMABLE T |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |

| CAN 1 MESSAGE CENTER 7 CONTROL REGISTER (C1M7C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CAN 1 MESSAGE CENTER 7 CONTROL REGISTER (C1M7C). CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M8C). CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M8C). CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M9C). EXTENDED INTERRUPT PERIORITY (EIP). CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M11C). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M11C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONT | B REGISTER (B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87                                                                              |

| CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M9C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CAN 1 MESSAGE CENTER 8 CONTROL REGISTER (C1M9C). CAN 1 MESSAGE CENTER 19 CONTROL REGISTER (C1M9C). CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M9C). EXTENDED INTERRUPT PRIORITY (EIP). CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M10C). EXTENDED INTERRUPT PRIORITY (EIP). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M14C). ADDENDUM TO SECTION 5: CPU TIMING. SYSTEM CLOCK SELECTION. CHANGING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY. ADDENDUM TO SECTION 6: MEMORY ACCESS EXTERNAL MEMORY INTERFACING. USING THE COMBINED CHIP-ENABLE SIGNALS. IMPLEMENTING A BOOTLOADER USING INTERNAL SRAM. EXAMPLE DS80C390 MEMORY CONFIGURATION. ADDENDUM TO SECTION 7: POWER MANAGEMENT.  11 POWER MANAGEMENT MODES. SWITCHING BETWEEN CLOCK SOURCES. 11 POWER MANAGEMENT MODES. 12 SWITCHING BETWEEN CLOCK SOURCES. 14 ADDENDUM TO SECTION 8: RESET CONDITIONS. 16 RESET SOURCES. 17 POWER CONFIGURATION. 18 RESET SOURCES. 19 POWER-ON/FAIL RESET. 10 WATCHOO'S TIMER RESET. 11 EXTERNAL RESET. 1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |

| CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M9C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CAN 1 MESSAGE CENTER 9 CONTROL REGISTER (C1M9C). CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M10C). EXTENDED INTERRUPT PRIORITY (EIP). CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M11C). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). ADDENDUM TO SECTION 5: CPU TIMING SYSTEM CLOCK SELECTION. CHANGINS THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY.  ADDENDUM TO SECTION 6: MEMORY ACCESS EXTERNAL MEMORY INTERFACING. USING THE COMBINED CHIP-ENABLE SIGNALS. MPLEMENTING A BOOTLOADER USING INTERNAL SRAM EXAMPLE DS80C390 MEMORY CONFIGURATION.  ADDENDUM TO SECTION 7: POWER MANAGEMENT.  10 POWER MANAGEMENT MODES. SWITCHING BETWEEN CLOCK SOURCES. 1 POWER-MANAGEMENT MODES. SWITCHING BETWEEN CLOCK SOURCES. 1 POWER-ON/FAIL RESET. 1 POWER TAYLE. 1 POWER RESET. 1 POWER-ON/FAIL RESET. 1 NATCHOOG TIMER RESET. 1 POWER STATE. 1 PORT 1 1 PORT 3 1 PORTS AND 5 1 OUTPUT FUNCTIONS. 1 PORTS AND 5 1 P |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |

| CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M10C).  88 EXTENDED INTERRUPT PRIORITY (EIP).  88 CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M11C).  89 CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M12C).  89 CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C).  89 CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M14C).  90 CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M14C).  90 CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  90 CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  90 CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  90 CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  91 SYSTEM CLOCK SELECTION 5: CPU TIMING  91 SYSTEM CLOCK SELECTION 5: CPU TIMING  92 CHANGING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY.  92 CADDENDUM TO SECTION 6: MEMORY ACCESS  93 USING THE COMBINED CHIP-ENABLE SIGNALS.  94 MPLEMENTING A BOOTLOADER USING INTERNAL SRAM  95 EXAMPLE OSSOC390 MEMORY CONFIGURATION.  95 CAMPLE OSSOC390 MEMORY CONFIGURATION.  96 SWITCHING SETTION TO SECTION 7: POWER MANAGEMENT.  100 POWER MANAGEMENT MODES  100 SWITCHING BETWEEN CLOCK SOURCES.  101 PUBLIC SETTION S. RESET CONDITIONS.  101 RESET SOURCES.  102 RESET SOURCES.  104 WATCHOOG TIMER RESET.  105 LEXTERNAL RESET.  106 LEXTERNAL RESET.  107 LEXTERNAL RESET.  108 LEXTERNAL RESET.  109 CRESET STATE.  100 PORT 1 POWER MADELE LI/O.  104 PORT 1 PORT 1 PORT 1 PROGRAMMABLE TIMERS.  106 DIVIDE-BY-13 OPTION.  110 PROGRAMMABLE CLOCK OUTPUT.  111 ADDENDUM TO SECTION 11: PROGRAMMABLE TIMERS.  106 DIVIDE-BY-13 OPTION.  111 ADDENDUM TO SECTION 12: SERIAL LI/O.  112 ADDENDUM TO SECTION 12: SERIAL LI/O.  113 ADDENDUM TO SECTION 13: TIMED ACCESS PROTECTION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CAN 1 MESSAGE CENTER 10 CONTROL REGISTER (C1M10C).  EXTENDED INTERRUPT PRIORITY (EIP).  CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M11C).  CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M12C).  CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C).  CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M13C).  CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  ADDENDUM TO SECTION 5: CPU TIMING.  SYSTEM CLOCK SELECTION.  CHANGING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY.  ADDENDUM TO SECTION 6: MEMORY ACCESS.  EXTERNAL MEMORY INTERFACING.  USING THE COMBINED CHIP-ENABLE SIGNALS.  IMPLEMENTING A BOOTLOADER USING INTERNAL SRAM  EXAMPLE DS80C390 MEMORY CONFIGURATION.  ADDENDUM TO SECTION 7: POWER MANAGEMENT.  11  POWER MANAGEMENT MODES.  SWITCHING BETWEEN CLOCK SOURCES.  11  ADDENDUM TO SECTION 8: RESET CONDITIONS.  11  RESET SOURCES.  12  POWER-ON/FAIL RESET.  WATOHOOG TIMER RESET.  EXTERNAL RESET.  13  RESET OUTPUTS.  RESET OUTPUT S.  RESET OU |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |

| EXTENDED INTERRUPT PRIORITY (EIP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EXTENDED INTERRUPT PRIORITY (EIP).  CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M12C).  CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C).  CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M12C).  CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M14C).  CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  ADBENDUM TO SECTION 5: CPU TIMING.  SYSTEM CLOCK SELECTION.  CHANGING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY.  ADDENDUM TO SECTION 6: MEMORY ACCESS  EXTERNAL MEMORY INTERFACING.  USING THE COMBINED CHIP-ENABLE SIGNALS.  IMPLEMENTING A BOOTLOADER USING INTERNAL SRAM  EXAMPLE DS80C390 MEMORY CONFIGURATION.  ADDENDUM TO SECTION 7: POWER MANAGEMENT.  11  POWER MANAGEMENT MODES.  SWITCHING BETWEEN CLOCK SOURCES.  12  ADDENDUM TO SECTION 8: RESET CONDITIONS.  14  RESET SOURCES.  15  POWER-ON/FAIL RESET.  16  WATCHOOG TIMER RESET.  17  WATCHOOG TIMER RESET.  18  EXERNAL RESET.  19  RESET STATE  11  IN-SYSTEM DISABLE MODE.  ADDENDUM TO SECTION 10: PARALLEL I/O.  11  PORT 1  PORTS 4 AND 5.  OUTPUT FUNCTIONS.  11  ADDENDUM TO SECTION 11: PROGRAMMABLE TIMERS.  11  INDIVIDE-BY-13 OPTION.  12  ADDENDUM TO SECTION 12: SERIAL I/O.  ADDENDUM TO SECTION 12: SERIAL I/O.  14  ADDENDUM TO SECTION 13: TIMED ACCESS PROTECTION.  15  16-BIT (8051 STANDARD) ADDRESSING MODE.  16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |

| CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M11C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CAN 1 MESSAGE CENTER 11 CONTROL REGISTER (C1M11C). CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M13C). CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  ADDENDUM TO SECTION 5: CPU TIMING.  SYSTEM CLOCK SELECTION CHANGING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY.  ADDENDUM TO SECTION 6: MEMORY ACCESS  EXTERNAL MEMORY INTERFACING USING THE COMBINED CHIP-ENABLE SIGNALS. IMPLEMENTING A BOOTLOADER USING INTERNAL SRAM EXAMPLE DSSBOC399 MEMORY CONFIGURATION.  ADDENDUM TO SECTION 7: POWER MANAGEMENT  POWER MANAGEMENT MODES  SWITCHING BETWEEN CLOCK SOURCES.  1 ADDENDUM TO SECTION 8: RESET CONDITIONS  11 RESET SOURCES. 10 POWER-ONLFALR RESET 11 WATCHOOG TIMER RESET 12 EXTERNAL RESET 11 RESET OUTPUTS 12 RESET STATE 11 RESET STATE 11 PORTS 4 AND 5. OUTPUT FUNCTIONS 11 DIVIDE-BY-13 OPTION 11 PORTS 4 AND 5. OUTPUT FUNCTIONS 11 ADDENDUM TO SECTION 11: PROGRAMMABLE TIMERS 11 DIVIDE-BY-13 OPTION 11 PORTS 4 AND 5. OUTPUT FUNCTIONS 11 ADDENDUM TO SECTION 12: SERIAL I/O. 11 ADDENDUM TO SECTION 12: SERIAL I/O. 11 ADDENDUM TO SECTION 13: TIMED ACCESS PROTECTION 11 ADDENDUM TO SECTION 13: TIMED ACCESS PROTECTION 11 ADDENDUM TO SECTION 15: INSTRUCTION SET DETAILS. 11 16-BIT (8051 STANDARD) ADDRESSING MODE. 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |

| CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M12C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CAN 1 MESSAGE CENTER 12 CONTROL REGISTER (C1M12C). CAN 1 MESSAGE CENTER 13 CONTROL REGISTER (C1M13C). CAN 1 MESSAGE CENTER 14 CONTROL REGISTER (C1M14C). CAN 1 MESSAGE CENTER 15 CONTROL REGISTER (C1M14C).  ADDENDUM TO SECTION 5: CPU TIMING. SYSTEM CLOCK SELECTION. CHANGING THE SYSTEM CLOCK/MACHINE CYCLE CLOCK FREQUENCY.  ADDENDUM TO SECTION 6: MEMORY ACCESS.  EXTERNAL MEMORY INTERFACING. USING THE COMBINED CHIP-ENABLE SIGNALS. IMPLEMENTING A BOOTLOADER USING INTERNAL SRAM. EXAMPLE DS80C390 MEMORY CONFIGURATION.  ADDENDUM TO SECTION 7: POWER MANAGEMENT.  11  POWER MANAGEMENT MODES. SWITCHING BETWEEN CLOCK SOURCES. 12  ADDENDUM TO SECTION 8: RESET CONDITIONS. 11  RESET SOURCES. 12  POWER-ON/FAIL RESET. 13  WATCHDOG TIMER RESET. 14  EXTERNAL RESET. 17  EXTERNAL RESET. 18  19  PORT 1  PORT 1  PORT 1  PORT 1  PORT 3  ADDENDUM TO SECTION 10: PARALLEL I/O. 11  ADDENDUM TO SECTION 11: PROGRAMMABLE TIMERS. 11  ADDENDUM TO SECTION 12: SERIAL I/O. 14  ADDENDUM TO SECTION 12: SERIAL I/O. 15  ADDENDUM TO SECTION 12: SERIAL I/O. 16  ADDENDUM TO SECTION 13: TIMED ACCESS PROTECTION. 17  ADDENDUM TO SECTION 13: TIMED ACCESS PROTECTION. 16  BORDOWN TO SECTION 16: INSTRUCTION SET DETAILS. 11  ADDENDUM TO SECTION 16: INSTRUCTION SET DETAILS. 11  16-BIT (8051 STANDARD) ADDRESSING MODE. 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CAN 1 MESSAGE CENTER 11 CONTROL DEGICE (C1M11C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88                                                                              |